前回に、DE10-Lite評価ボードを使用して、4時間をカウントする機能を作成しました。前回の内容は下記を参照してください。

24時間カウンタ機能の仕様は下記の通りです。

- DE10-Liteには、7セグメントが6個用意されています。

- その中の2個ずつを、秒、分、時に割り当てます。

- Resetボタンを押すと、00時00分00秒になります。

- 24時間になった場合、00時00分00秒になります。

今回は、DE10-Lite評価ボードを使用して、24時間をカウントする機能を改良していきたいと思います。今回も使用する言語は、VHDLです。前回述べたのように、機能的には問題ないと思いますが、カウンタのズレが発生していると思います。

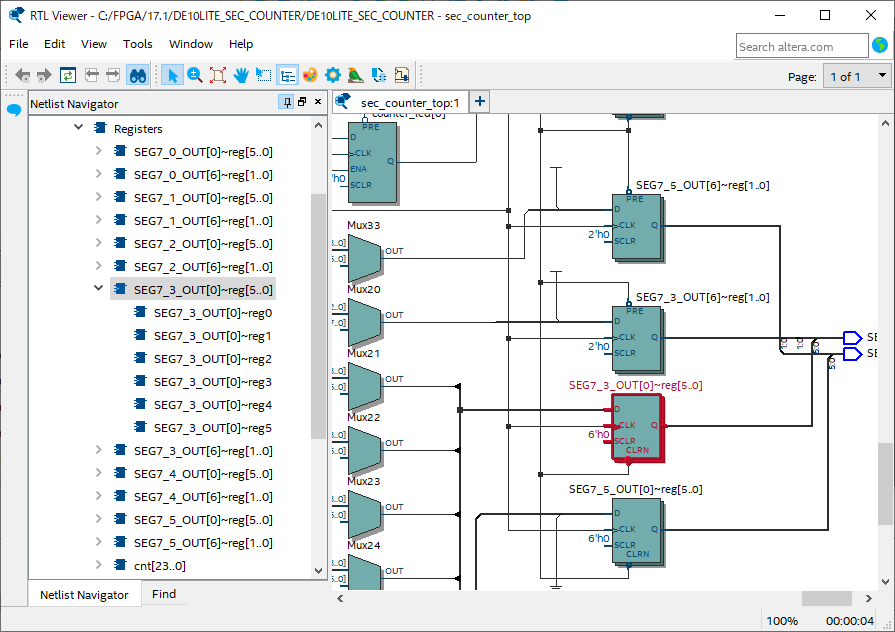

例えば、7セグメントに信号を送る処理をprocess処理のcase文で行っていますが、ここもカウンタが更新されて1クロック遅れて更新されていると思いわれます。下記のように回路図でみるとレジスタから出力されています。そのため、1クロック遅れていると思います。

今回は、ここらへん内容を改良していきたいと思います。それでは、改良していきたいと思います。

前回のプロジェクトファイルを開いて、下記のようにVHDLファイルを改良しました。