前々回に、下記のFPGA(MAX10)基板を使用して、LEDの点滅回路を作成しました。

前々回の内容は下記を参照してください。

FPGA MAX10(2)-LED点滅回路

今回は、DE10-Lite評価ボードを使用して、LEDの点灯をシフトする機能を作成しようと思います。前々回はVerilog HDL言語を使用していましたが、今回はVHDL言語を使用したいと思います。

LED点灯シフト機能の使用は下記の通りで、シンプルです。

DE10-Liteには、赤色LEDが10個(LED0~LED9)が用意されています。 1秒経過するごとに、LED0→LED1→・・・→LED8→LED9→LED0→・・・変化させます。

DE10-LiteにはPushSwitchが2個(KEY0、KEY1)が用意されています。KEY0ボタンを押すと、LED0が点灯するようなリセット動作をします。

クロックカウンタもリセットさせます。

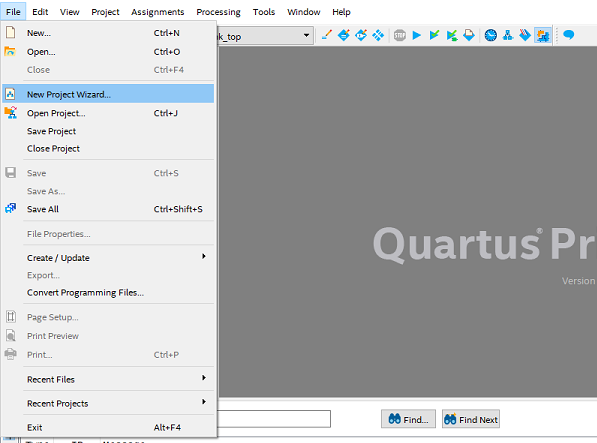

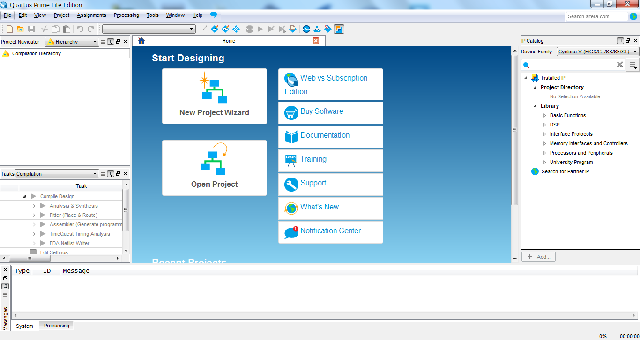

それでは、機能を構築していきたいと思います。まずは、新規プロジェクトを作成します。メニューから「File」→「New Project Wizard」を選択します。

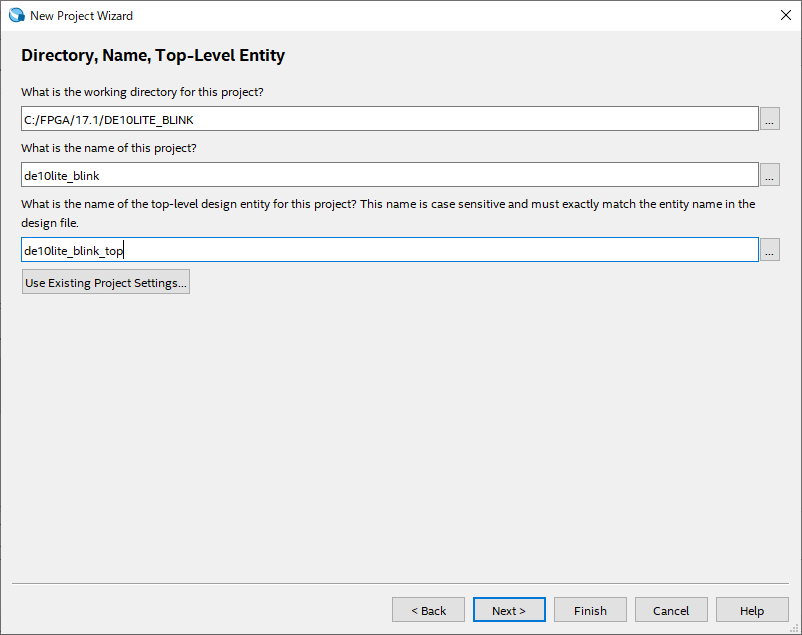

下記のような画面が表示されるので、プロジェクトの保存先、プロジェクト名、トップエンティティ名をを入力して、「Next」ボタンを押します。

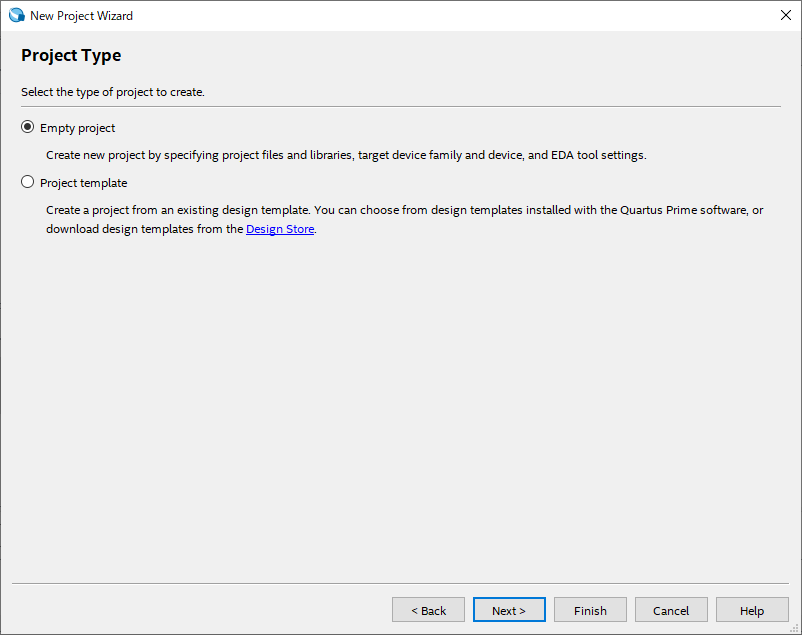

下記のような画面が表示されるので、プロジェクトタイプを選択します。今回は、Empty projectを選択して、「Next」ボタンを押します。

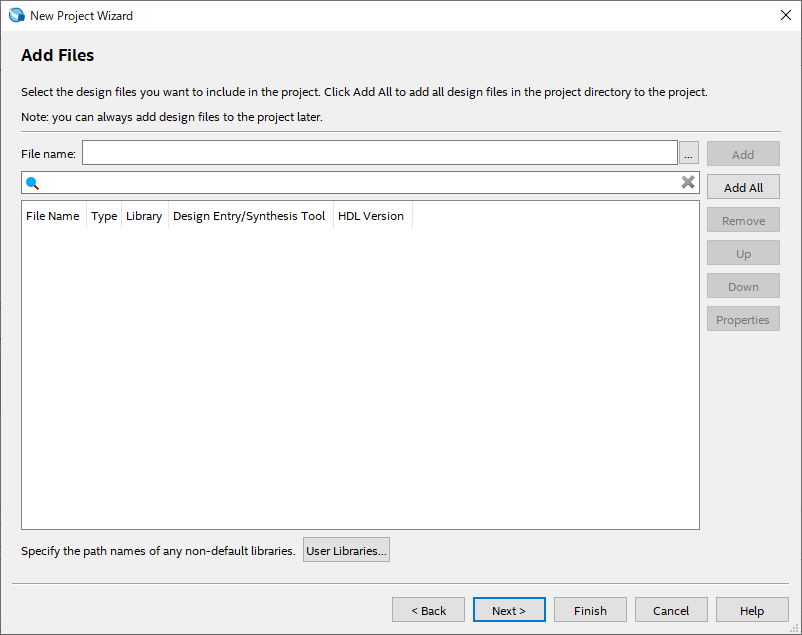

下記のような画面が表示されるので、追加したいファイルを選択します。今回は追加ファイルはないので、そのまま「Next」ボタンを押します。

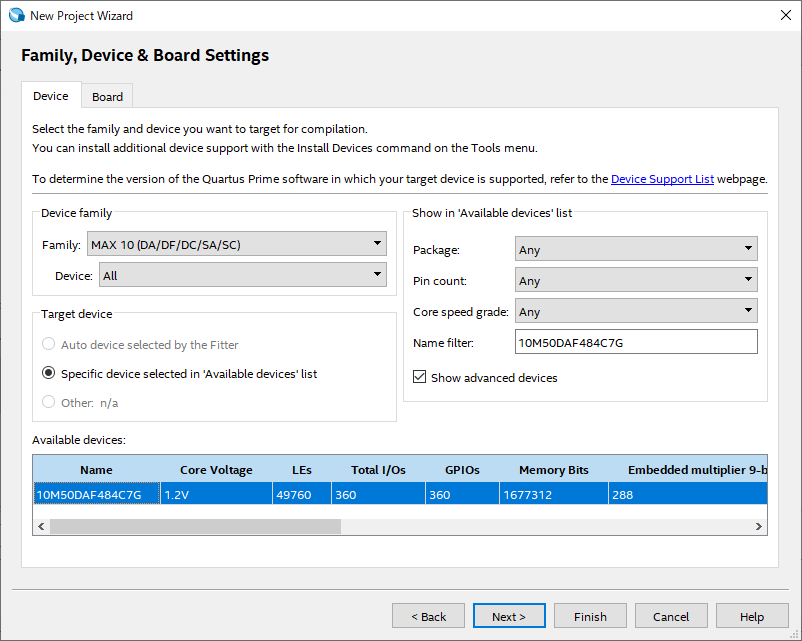

下記のような画面が表示されるので、使用するFPGAを選びます。DE10-Liteには、「10M50DAF484C7G」が搭載されているので、「Available devices:」から選択して、「Next」ボタンを押します。

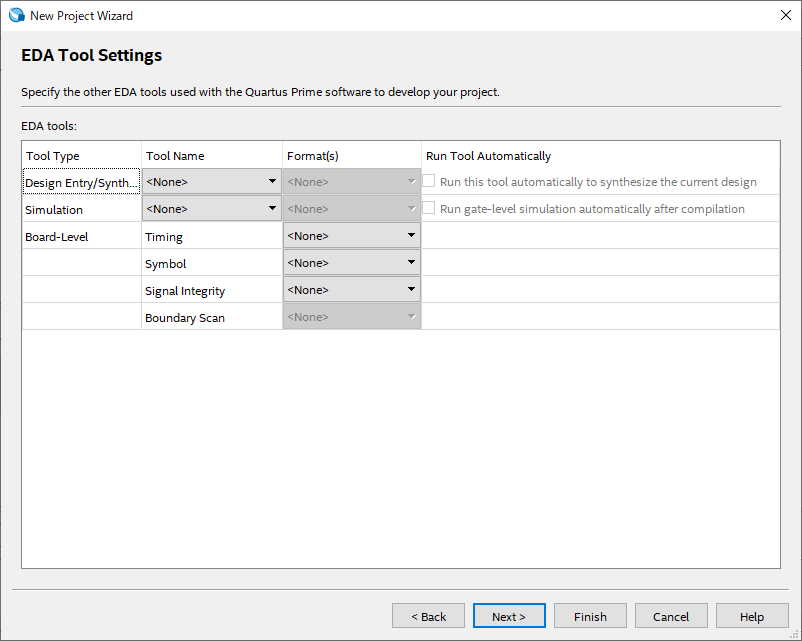

下記のような画面が表示されるので、EDAツールの設定を行います。今回はとくに設定は行わないので、そのまま「Next」ボタンを押します。

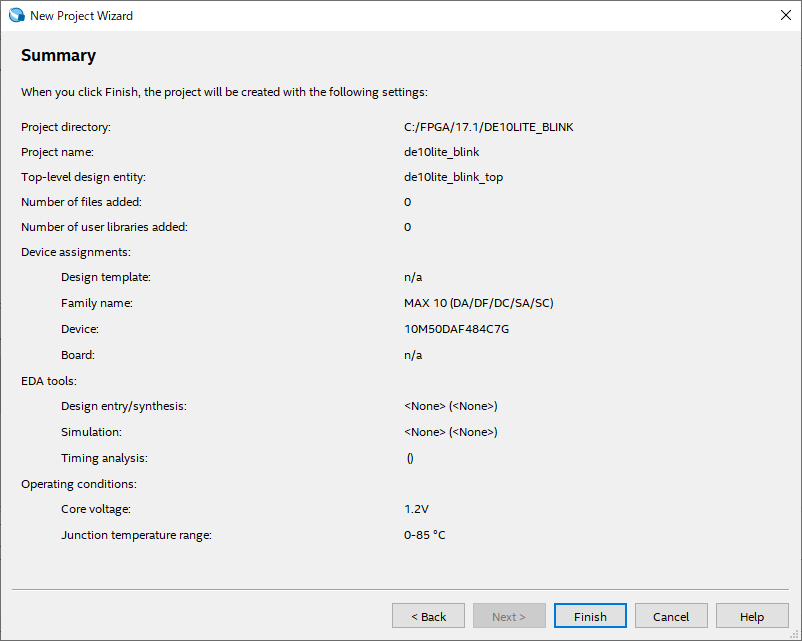

下記のような画面が表示されるので、設定した内容を確認して問題なければ、「Finish」ボタンを押します。

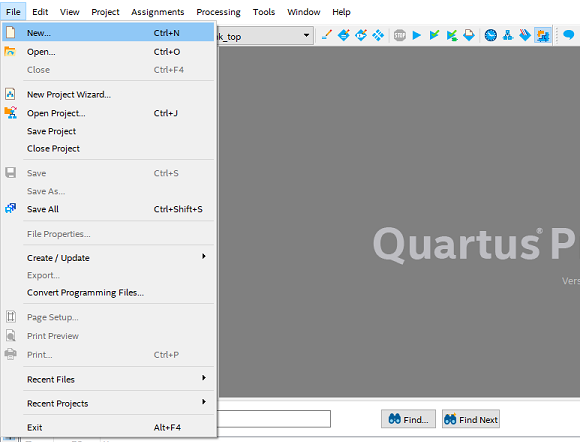

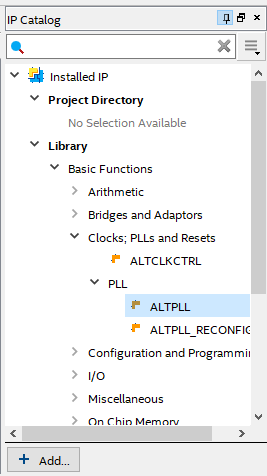

これでプロジェクトファイルの作成が完了したので、次にVHDLファイルを追加します。メニューから「File」→「New」を選択します。

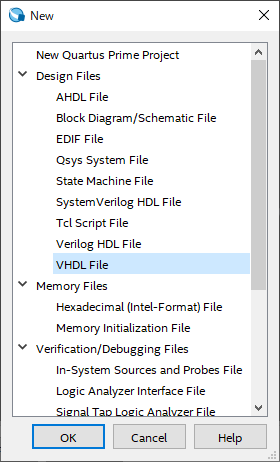

下記のようが画面が表示されるので、「VHDL File」を選択して、「OK」ボタンを押します。

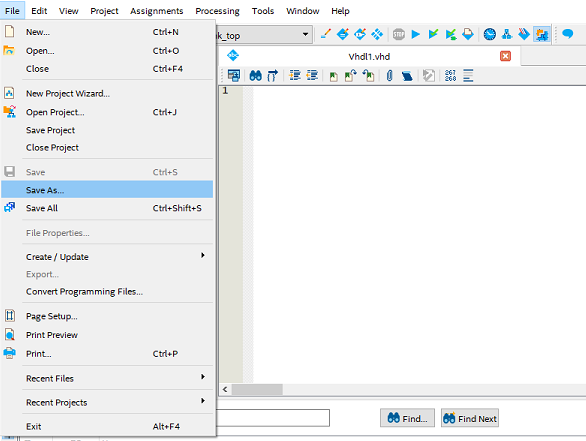

VHDLファイルが作成できたので、ファイルから「File」→「Save As」を選択して、名前を付け保存します。

ファイル名を入力(任意名)して、「保存」ボタンを押します。

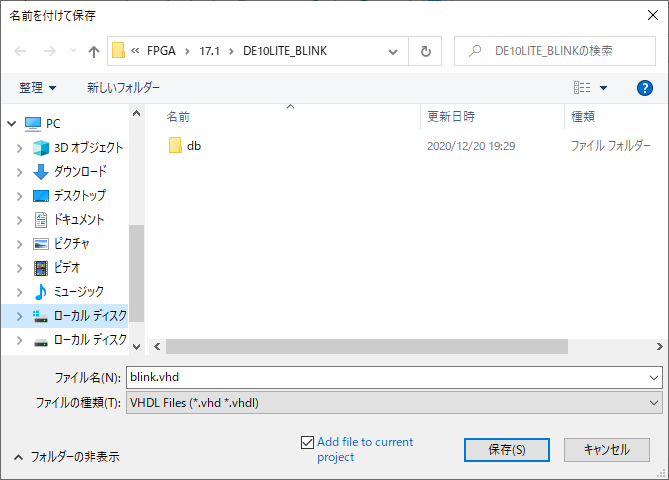

クロックの設定を行っていきます。DE10-Liteのクロックは下記のようになっています。クロックジェネレータから生成されたクロックがMAX10に供給されています。今回、P11に供給されるクロックを使用しようと思います。50MHzになりますが、今回は、PLLで10MHzを生成して使用しようと思います。

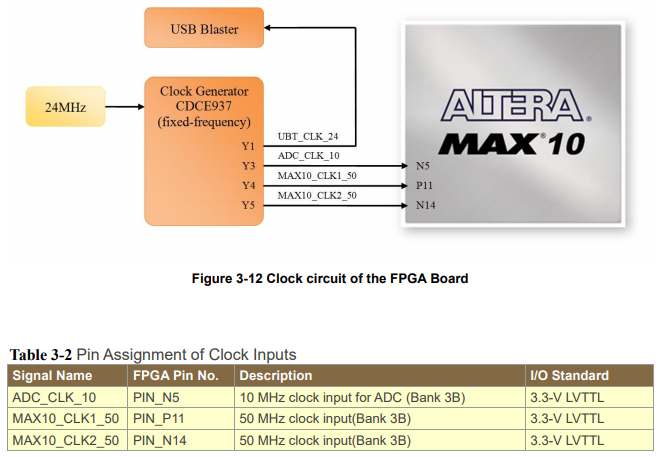

今度は、IPを使用して、PLLを追加します。IP Catalogから「Installed IP」→「Library」→「Basic Functions」→「Clocks; PLLs and Resets」→「PLL」→「ATLPLL」を選択します。

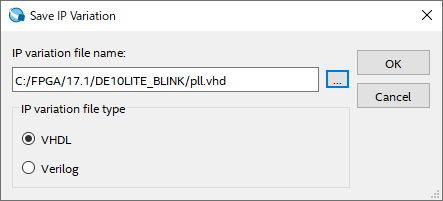

下記のような画面が表示されるので、生成されるIPのファイル名を設定します。ファイルタイプは「VHDL」を選択してOKボタンを押します。

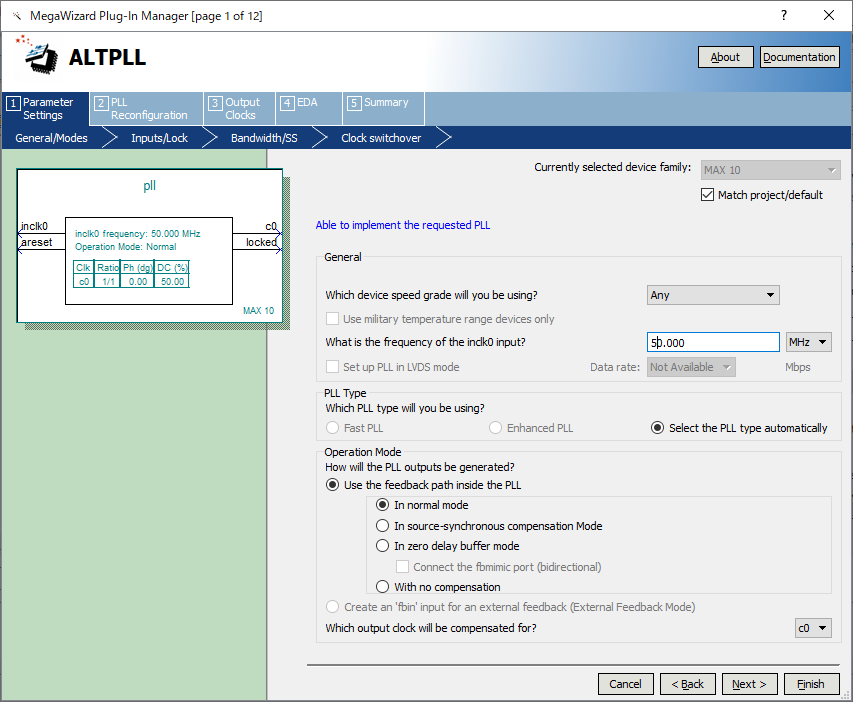

ALTPLLのウィーザードが表示されました。ウィザードに従って設定をしていきます。「What’s the frequency of the inclk0 input?」に「50.000MHz」を入力して、「Next」ボタンを押します。

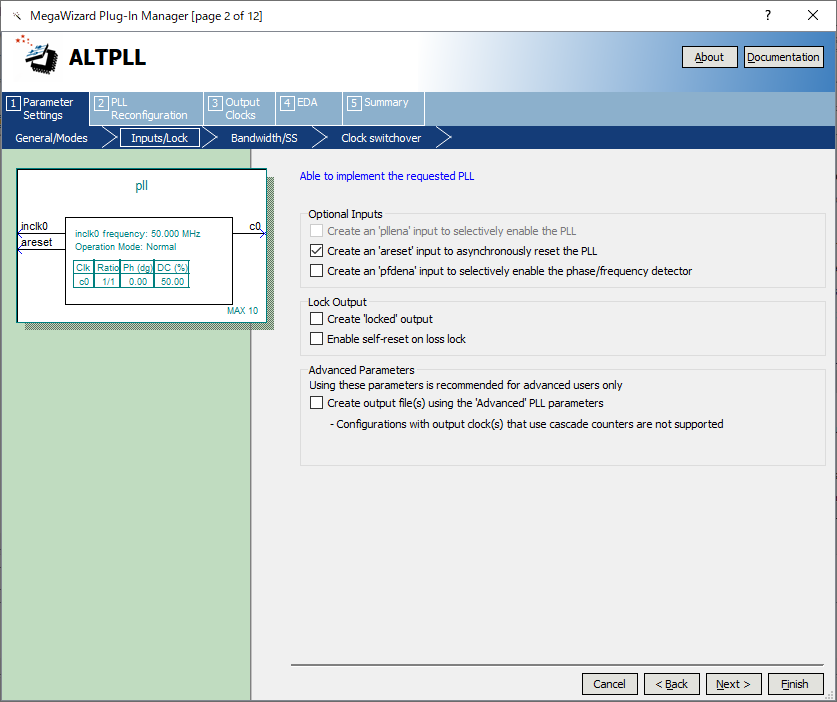

「Create an ‘areset’ input to asynchronously reset the PLL」にチェックを入れて「Next」ボタンを押します。

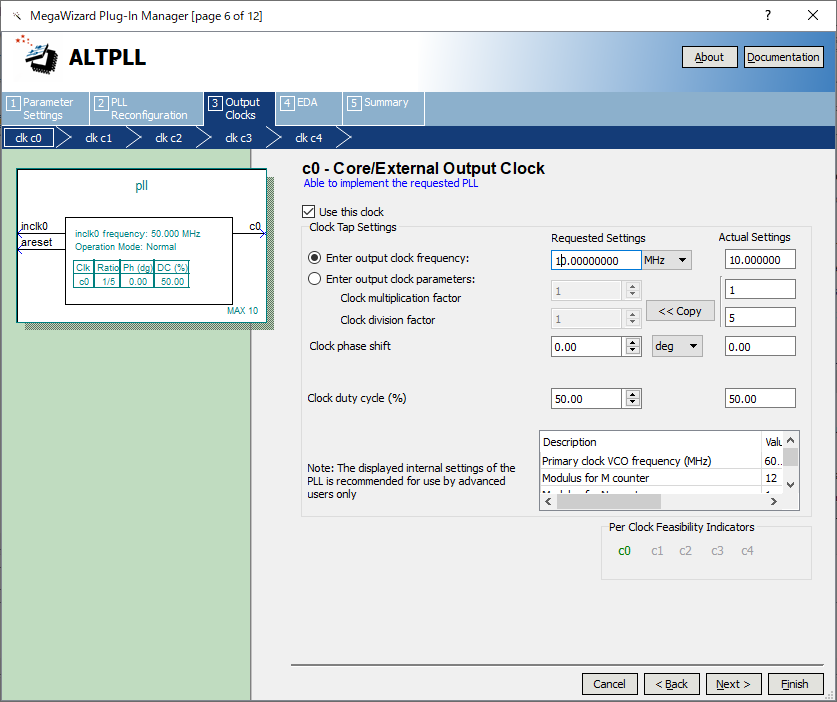

「Output Clocks」のタブになるまで「Next」ボタンを押していきます。c0の設定画面が開かれたら、「Use this clock」にチェックを入れて、c0を有効にします。「Enter output clock frequency」にチェックを入れて、「10.000MHz」を入力して、「Next」ボタンを押します。

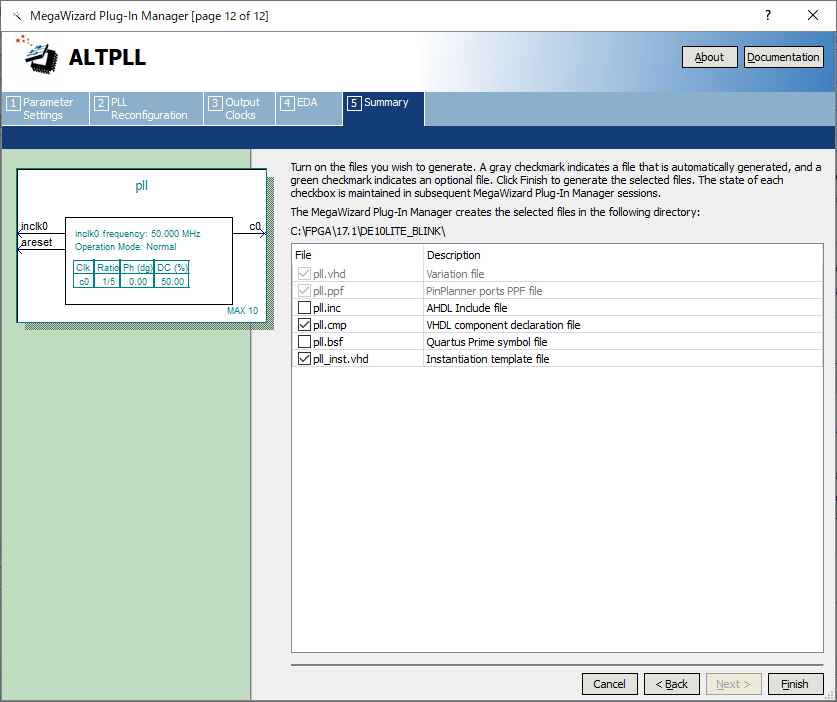

「Summary」のタブになるまで「Next」ボタンを押していきます。「Summary」が開かれたら、「pll.cmp」「pll_inst.vhd」を選択して「Finish」ボタンを押します。

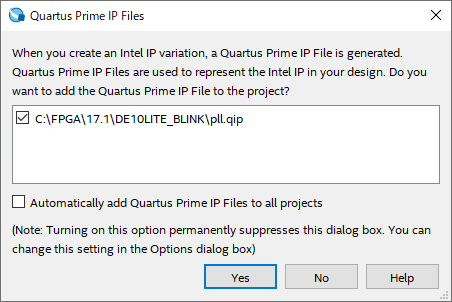

プロジェクトにIPを追加したいですかと問われているので、「Yes」ボタンを押します。

これでPLLが追加されたので、それでは、先程新規作成したVHDLファイルに動作内容を記述していきます。下記のように記述しました。

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

use IEEE.std_logic_arith.all;

entity de10lite_blink_top is -- Output pin

port(

CLK : in std_logic; -- 50MHz Clock

RST_N : in std_logic;

LED_OUT : out std_logic_vector(9 downto 0)

);

end de10lite_blink_top;

architecture rtl of de10lite_blink_top is -- Internal process

component pll is -- pll

port(

inclk0 : in std_logic; -- 50MHz Clock

c0 : out std_logic -- 10MHz Clock

);

end component;

signal s_clk : std_logic; -- 10MHz Clock signal

signal en : std_logic;

signal cnt : std_logic_vector(23 downto 0);

signal counter_led : std_logic_vector(9 downto 0);

begin

u0_pll : pll

port map(

inclk0 => CLK, --in std_logic(50MHz)

c0 => s_clk --out std_logic(10MHz)

);

en <= '1' when (cnt = X"989680") else '0'; -- 1sec

process(s_clk, RST_N) -- s_clkに変化があった時

begin

if(RST_N = '0')then

cnt <= (others=>'0'); -- cnt全部「0」※othersはそれ以外の意

elsif(s_clk'event and s_clk = '1')then -- s_clk 変化有り 且つ s_clk = 1の時 →クロックの立ち上がりエッジ

if(en = '1')then -- 1msec

cnt <= (others=>'0'); -- cnt全部「0」※othersはそれ以外の意

else

cnt <= cnt + '1';

end if;

end if;

end process;

process(s_clk, RST_N)

begin

if(RST_N = '0')then

counter_led <= "0000000001";

elsif(s_clk'event and s_clk = '1')then -- s_clk 変化有り 且つ s_clk = 1の時 →クロックの立ち上がりエッジ

if(en = '1')then

counter_led(1) <= counter_led(0);

counter_led(2) <= counter_led(1);

counter_led(3) <= counter_led(2);

counter_led(4) <= counter_led(3);

counter_led(5) <= counter_led(4);

counter_led(6) <= counter_led(5);

counter_led(7) <= counter_led(6);

counter_led(8) <= counter_led(7);

counter_led(9) <= counter_led(8);

counter_led(0) <= counter_led(9);

end if;

end if;

end process;

LED_OUT <= counter_led;

end rtl;

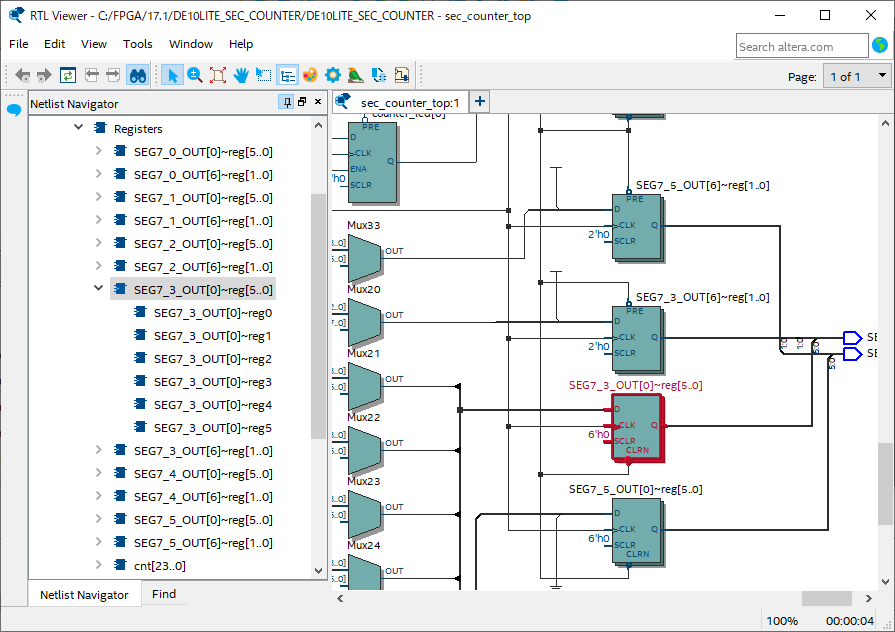

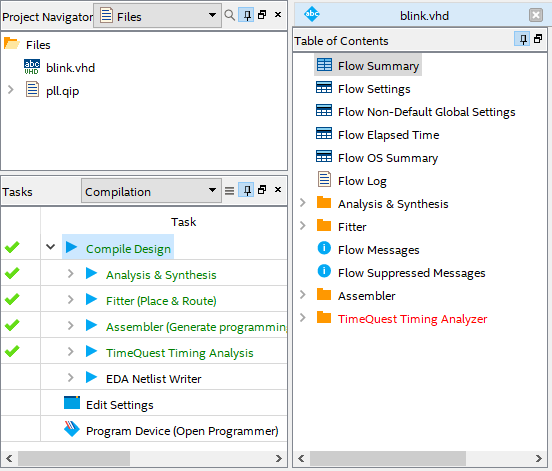

次に、Tasksから「Compile Design」をダブルクリックして実行します。(「Analysis & Synthesis」のみ実行してもよいと思います。)

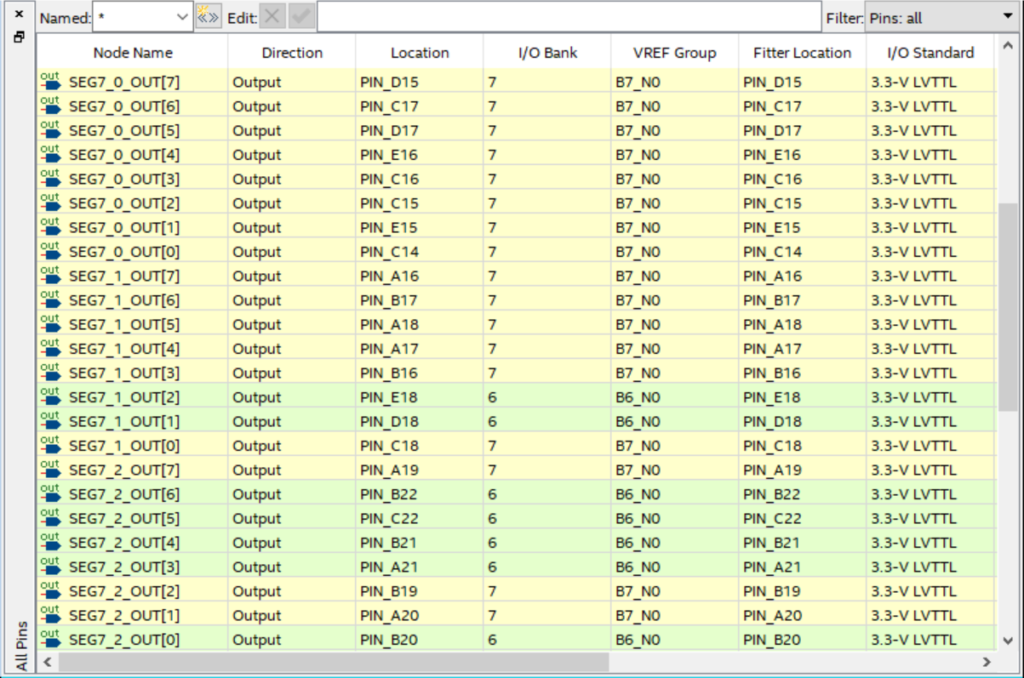

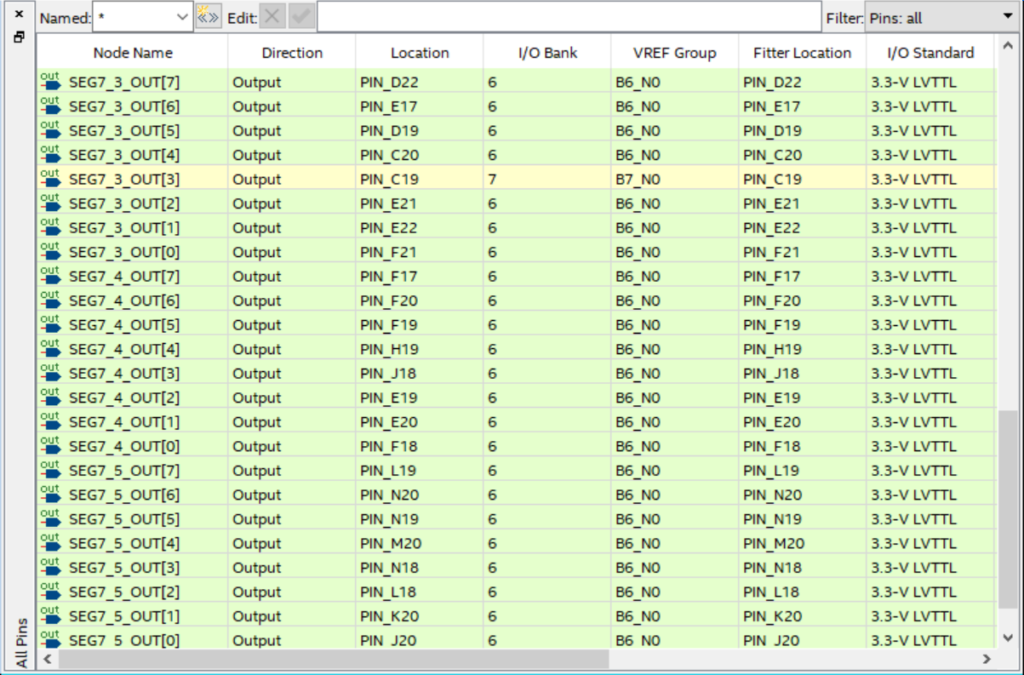

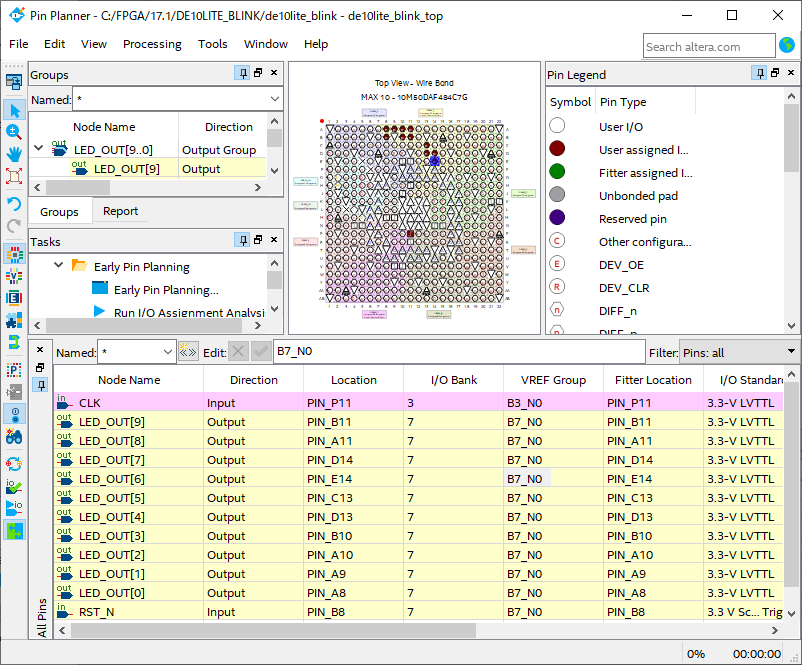

「Compile Design」が成功したら、ピンの設定をします。メニューから「Assignments」→「Pin Planner」を選択します。ピンの設定を行う画面が表示されるので、下記のようにピンを設定します

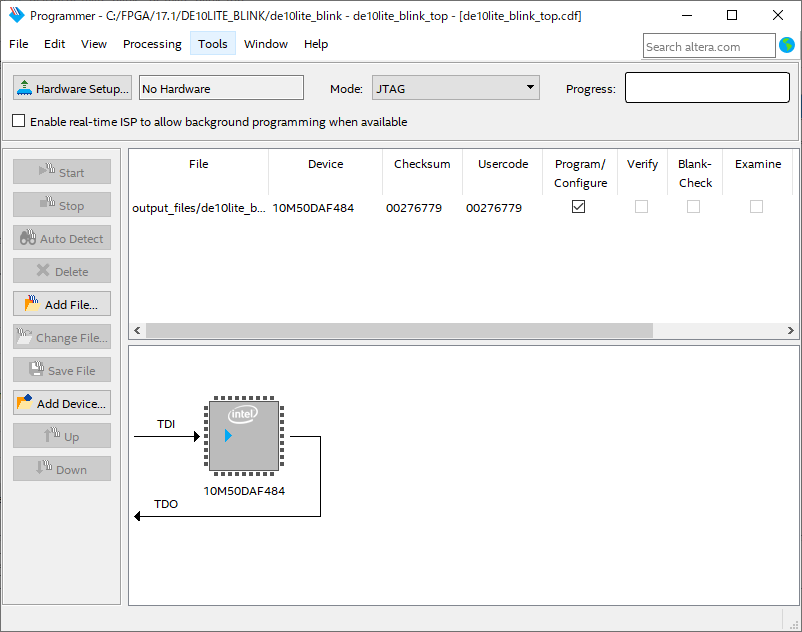

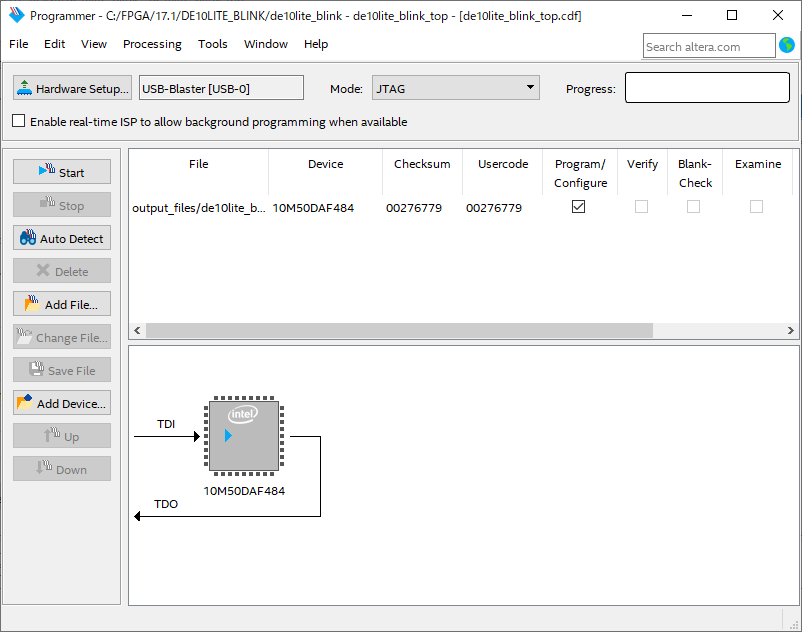

それでは、再度、Tasksから「Compile Design」をダブルクリックして実行します。「Compile Design」が成功したら、書き込みを行います。メニューから「Tools」→「Programmer」を選択します。下記のような画面が表示されるので、「Hardware Setup」ボタンを押します。

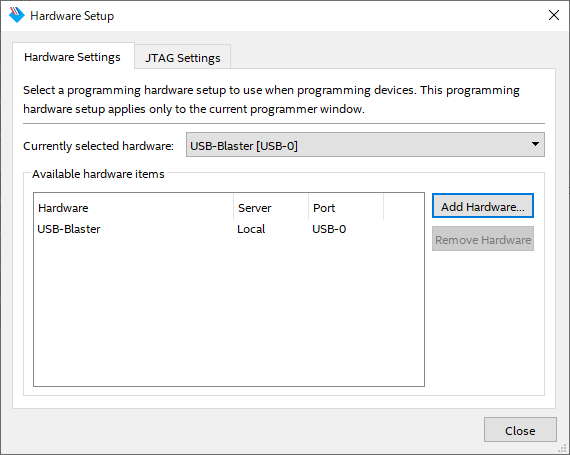

「Currently selected hardware」より「USB-Blaster[USB-*」を選択します。選択したら「Close」ボタンを押します。

「Start」ボタンを押して書き込みを行います。

1秒経過するごとに、LED0→LED1→・・・→LED8→LED9→LED0→・・・とLEDがシフトして点灯しています。KEY0ボタンを押すと、LED0が点灯しました。